艾崴安檢機是如何高速的采集X光立體透視圖像數據的?

作者: / / 閱讀人數:24

對於艾崴100100客運站全功能型X光集裝箱安檢機來說,要高速汽車掃描采集出高清的X光透視畫麵,就需要X光射線源與X光探測器即時的上電,並通過FPGA圖像數據傳輸板準確地與工業控製計算機的CPU主板建立高速圖像數據通信。想象一下,如果采集的圖像細節重複數據量很大,或者傳輸幹擾太多,那怎麽能順利的處理出高清晰的X光圖片呢。武漢艾崴科技有限公司研發人員為這套X光集裝箱安檢機圖像采集、 傳輸、 處理、 控製專門設計了一套時序控製電路信號傳輸通道,為汽車掃描采集出高清晰的X光像片建立了高速的信號通道專線。為後麵的圖像危險物辨識提供了重要技術保障。

X光高清透視效果圖

在艾崴X光集裝箱安檢機係統中,X光探測器與圖像處理工業控製計算機的雙向通訊具有非對稱性,由X光探測器采樣汽車掃描得到的大量圖像BIT數據通過高速通道傳送至圖像處理工業控製計算機進行處理。然而由圖像處理工業控製計算機傳送給X光探測器的控製信號,因數據量較小,僅需低速通道進行傳輸即可,並且在X光探測器數據傳輸板對於高速大量圖像BIT數據的處理是基於FPGA平台實現的,若同時采用單片FPGA對接收控製信號進行處理,一方麵可減少硬件電路的設計負擔,另一方麵也降低了設備本錢。但與此同時,若該係統采用傳統串行通訊方式,則在處理高速數據的FPGA電路單元中引進低速時鍾線,不僅輕易受到電路板上高頻信號的影響,而且由於圖像處理工控電腦間隔X光探測器間隔較長,不利於時鍾信號的傳輸。因此,對於X光集裝箱安檢機控製信號的傳輸一般采用單路串行低速通訊方式。對於這種傳輸方式,在FPGA上采用一種高效的數字時鍾提取技術就十分必要。

X光圖像數據高速傳輸模似圖

1 X光傳輸板FPGA數字時鍾提取環路基本原理

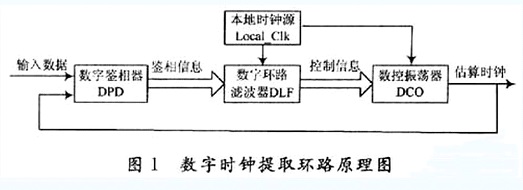

數字鎖相環能讓本地產生的時鍾信號自動跟蹤輸進信號相位,從而實現一個閉環自動控製係統。數字鎖相環的基本結構是由數字鑒相器(DPD)、數字環路濾波器(DLF)、數字可控振蕩器(DCO)和本地時鍾源(LC)組成的一個反饋環路,其具體原理框圖如圖1所示。

基於數字鎖相環的數據時鍾提取係統工作原理如下:本地產生一個高頻率的時鍾,數字鑒相器通過輸進信號與估算時鍾進行鑒相比較,輸出鑒相信息。之後由數字環路濾波器根據鑒相信息對相位誤差進行平滑運算,輸出數控振蕩器控製信號,通過對本地估算時鍾的相位調整,終極跟蹤到輸進數據的位同步時鍾。

2 各模塊功能及實現原理

2.1 數字鑒相器

數字鑒相器用於獲取輸進信號與本地估算時鍾的相位比較信息,常用異或門實現。在數字鑒相器中,首先將輸進信號的正向過零脈衝與本地估算信號的正向過零脈衝進行比較,從中得到一個表明相位提前或延後誤差的脈衝輸出,其寬度反映超前(滯後)相位的多少。當本地估算信號超前於輸進信號時,其輸出為超前脈衝,反之,則為滯後脈衝。綜合考慮到安檢係統中的控製信號屬於數字信號,並且由於X光集裝箱安檢機傳輸板FPGA的資源主要用於完成采集數據的處理,應盡量減少對X光集裝箱安檢機FPGA資源的使用。艾崴IWILDETECTOR采用了超前/滯後數字鑒相器。

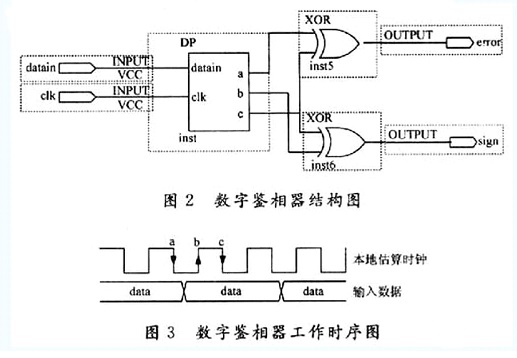

超前/滯後數字鑒相器硬件實現有兩種方式,分為積分型結構與微分型結構。積分型結構的硬件實現比較複雜,但具有良好的抗幹擾性能;微分型結構則具有相反特性。為了優化係統性能,選擇使用微分型結構。盡管微分型結構的抗幹擾能力較弱,但是結合集裝箱安檢機係統的實際環境,該結構可以滿足係統需要。圖2為微分型超前/滯後數字鑒相器的結構原理圖,

圖3為其時序圖。

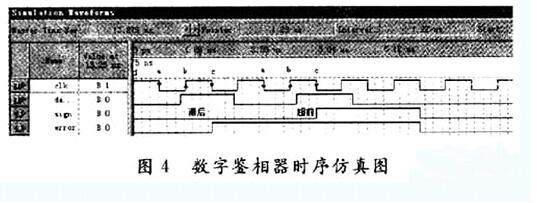

通過期序圖可以看到,輸進數據datain在本地估算時鍾的邊沿(包含上升沿和下降沿)觸發下,依次存進寄存器a,b,c中。在時鍾下降沿的觸發下,通過對a,c信號進行異或運算,天生error信號,作為誤差跳變盡對值輸出。通過對b,c信號進行異或運算,天生sign信號,作為超前/滯後標誌位輸出。具體仿真結果如圖4所示。

從圖4可以發現,對於error信號,若前一位數據存在跳變,則輸出高電平,否則輸出低電平。對於sign信號,當估算時鍾超前時,輸出高電平,滯後時,輸出低電平。該模塊輸出的兩路信號將作為環路濾波器的輸進信號,對下級結構進行控製。

2.2 數字環路濾波器

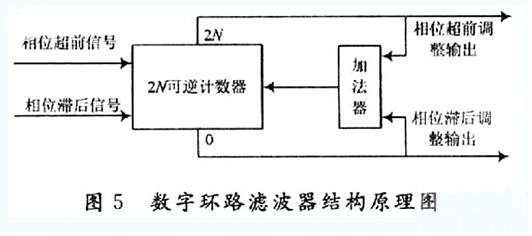

數字環路濾波器在鎖相環路係統中主要起兩種作用:其一,輸出超前調整信號及滯後調整信號,以控製數控振蕩器模塊,對估計時鍾進行相位調整;其二,有數字濾波作用,對噪聲信號及高頻幹擾信號起到較好的抑製作用。數字環路濾波器內部擁有容量為2N的計數器,能夠有效消除隨機出現的具有正態分布特性的噪聲信號。容量2N值越大,對噪聲抑製效果越好,但同時2N值越大,跟蹤速度越慢,實時捕捉能力下降。所以設計時,2N值的選取要綜合考慮安檢係統的實際參數要求。出於減少占用X光集裝箱安檢機FPGA係統資源的考慮,該係統采用隨即徘徊濾波器作為實現方案。

該濾波器原理框圖如圖5所示。

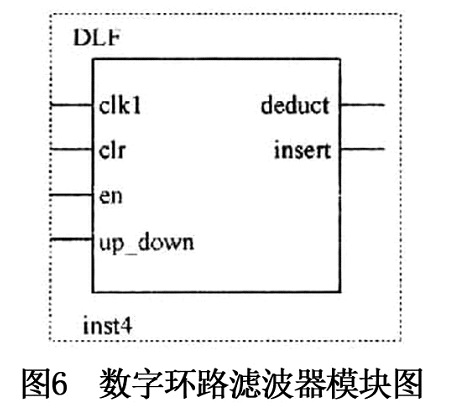

在實現方案中,環路濾波器通過加減計數邏輯單元實現。通過讀取鑒相單元輸出的兩路使能信號對計數器進行代數累加或累減操縱,當達到記數的邊界值0或2N時在輸出端送出insert(插進時鍾周期)或deduct(扣除時鍾周期),與此同時,計數器內部寄存器值從2N自動恢複到N,重新開始。

該模塊如圖6所示,其中clkl是記數時鍾,由數控振蕩器模塊內部分頻得到;clr是啟動清零控製端;en接前端模塊的error信號,該引腳是對記數功能的使能,即在輸進數據(Data_in)有跳變時,才能判定相位誤差;up_down是加減記數輸進,與上級模塊的sign使能信號相連,當sign=1時,做累加操縱,當sign=0時,做累減操縱,直到代數累加/累減運算到0或2N時,再對累加/累減計數器進行恢複。

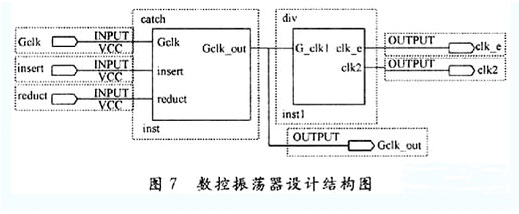

catch模塊的功能如下:

在IWILDETECTOR係統中,X光集裝箱安檢機FPGA傳輸板上用於驅動高速采樣數據發送的主時鍾為64 MHz,因此本設計中的全局時鍾Gclk頻率為64 MHz,這樣可以有效節約X光集裝箱安檢機FPGA傳輸板上的硬件PLL資源,進步了硬件使用效率。

在catch模塊內部,首先對全局時鍾Gclk進行4分頻,由於Gclk的設計頻率為64 MHz,實現4分頻後達到16 MHz。之後,catch模塊根據前端環路濾波器的輸出信號insert和reduct,在分頻後的16 MHz時鍾推動下,若insert信號出現高脈衝,自動在4分頻後的時鍾上補充一個Gclk時鍾周期的延時,該操縱僅對insert信號的高脈衝上升沿有效;相類似,若reduct信號出現高脈衝,自動在4分頻後的時鍾上扣除一個Gclk時鍾周期。

div模塊的功能如下:

該模塊為catch單元的後級,其主要功能是根據catch給出的Gelk_out信號進行N分頻。在本係統中,需要恢複頻率為4 MHz的數據時鍾,因此這裏第一個分頻係數N=4,輸出為1*=4 MHz的時鍾信號(clk_e),第二個分頻時鍾為數字環路濾波器的記數時鍾,該信號是經過2分頻(頻率為8 MHz)後的時鍾信號,用於進行DLF濾波。與此同時,也可以加速該時鍾,這樣可以縮短捕捉時間,並且擴展其捕捉帶寬。

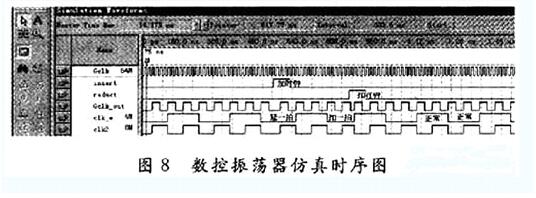

該數控振蕩器的加扣時鍾和分頻的綜合仿真時序圖如圖8所示。

從該時序圖可以看到,在insert與reduct信號的控製下,模塊內部進行加/減時鍾操縱,終極在輸出時鍾信號中得到延時或者扣除節拍的捕捉效果。

3 本係統整體時序仿真結果

結合集裝箱安檢機控製信號的實際傳輸情況,確定設計要求,對整體係統進行時序仿真。其中,選定Gclk頻率為64 MHz,數據速率為4 Mb/s,並設定初始狀態中,估計時鍾和數據的相位差為103.775 ns,顯示結果為相位滯後。根據數字鎖相環的基本原理,必須進行扣脈衝的操縱後才能終極提取到同步時鍾。鑒於該係統需要的捕捉精度較高,因此捕捉時間較長,並且由於整個仿真界麵有限,隻能觀察到時鍾提取過程,具體如圖9所示。

由圖9可以看出,從箭頭處開始,出現了扣脈衝和加脈衝循環出現的情況,對於該情況分析如下:

由於初始設定的估計時鍾相位滯後為103.775 ns,從圖9仿真結果可以看出,在經曆了7次扣脈運算後,由於每次扣脈衝的時間是1/(64×106)=15.225 ns,那麽7個扣脈衝的時間就是15.225 ns×7=106.575 ns。在7個時鍾扣除以後,相位又超前了106.575-103.775=2.8 ns,因此後續的操縱必須加脈衝,從而實現相位捕捉。由於每加一個脈衝是15.225 ns,之後會再次出現相位滯後,又進行扣脈衝操縱。如此循環,直到終極接近極限,提取到穩定的時鍾信號。

4 X光集裝箱安檢機FPGA傳輸板硬件測試

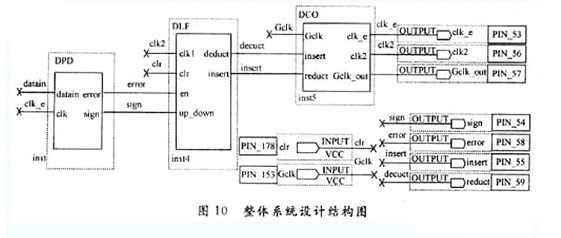

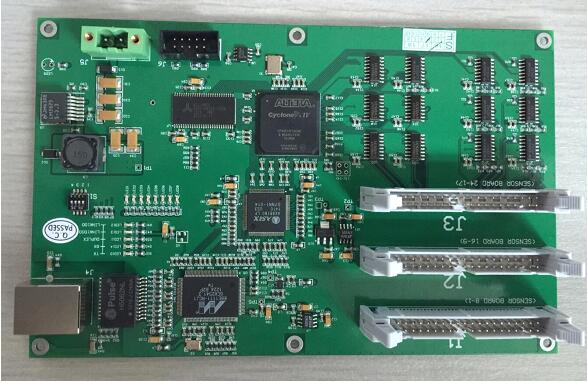

鑒於艾崴IWILDETECTOR X光集裝箱安檢機FPGA傳輸板係統應用於X光集裝箱安檢機控製信號傳輸係統中,故將該設計通過FPGA硬件平台進行了驗證。該驗證平台基於Altera公司Cyclone係列的EPlCl2Q240C8型號的FPGA芯片。鑒於實際係統中FPGA的本地係統時鍾為32.768 MHz,故測試輸進數據(datain)的速率為4.096 MHz。基於FPGA開發軟件Quartus實現的測試係統整體結構圖如圖10所示。

Signal TapⅡ邏輯分析器是Quartus軟件中集成的一個內部邏輯分析軟件,使用它可以觀察設計的內部信號變化,為FPGA設計的調試、開發帶來極大的方便,實用性很高。以下各圖為Quartus軟件中SignalTapⅡ實時觀察到的數據。

相位調整驗證

如圖11所示。由圖11可以發現,開始時鍾的相位滯後於數據相位。因此經過調整,通過數字環路濾波器輸出的reduct信號控製數控振蕩器模塊進行扣時鍾操縱,終極使本地估算時鍾與數據時鍾同步,正確地調整了相位。

當該係統捕捉到數據時鍾後,就會穩定輸出與數據信號同相的時鍾信號,穩定狀態截圖如圖12所示。

利用FPGA開發平台所具有的Signal TapⅡ功能,成功地在硬件平台上驗證了該係統的可行性與穩定性。

艾崴X光集裝箱安檢機圖像數據傳輸板

同時,為保證X光圖像采集數據的高保真傳輸,在FPGA圖像傳輸板中,武漢艾崴科技有限公司基於鎖相環的實現方案不僅優化了時鍾提取的精度,而且平衡了捕捉時間,為X光集裝箱安檢機係統低速控製信令的傳輸提供了基本的技術支持,並且使高速圖像數據傳輸僅需要一條UTP-5的網線就可以完全實現,保證了X光集裝箱安檢機控製信號與圖像數據鏈路傳輸的高效性,提高了X光集裝箱安檢機硬件整體係統的運行效率

艾崴IWILDETECTOR X光集裝箱安檢機硬件係統中經曆了從電性件、鑒定件、工藝試驗件直到正樣4個階段產品的反複加工、調試、性能測試,先後開展了力學、熱控、溫度、濕度以及功率容量等多項試驗驗證,充分保證了在高鐵站火車站客運站安檢長進間運行的的可靠性。